綠能原生適應性電壓定位架構 (G-NAVP™) 的 CPU 電源解決方案

摘要

隨著中央處理單元(CPU)的發展,對CPU電源供應的要求也越來越嚴格。然而,立錡早已長期投入 CPU 電源供應的應用開發,並已提出了許多

CPU 的電源解決方案,使能滿足每一代 CPU 對電源的需求。本應用須知將介紹一屬於立錡專利的 CPU 電源解決方案,即綠能原生適應性電壓定位 (G-NAVP™)

控制架構。 G-NAVP™ 控制架構具有快速響應、高效率的特色,而且幾乎可滿足所有 CPU 電源規格的要求,所以目前 G-NAVP™

控制架構是已被廣泛採用的CPU電源解決方案。

1. CPU 電源規格之簡介

1.1.微處理器 (中央處理單元: CPU)

微處理器(中央處理單元:CPU)廣泛地使用於許多應用中,諸如計算機系統,嵌入式系統,和手持裝置等。而為了提升微處理器的性能,往往將更多電晶體整合在微處理器裡。然而,隨著半導體製造技術的提高,晶片尺寸反而降低。自從英特爾

(Intel) 微處理器 4004 在1971年首次發佈以來,整合的電晶體數量大致是按照摩爾定律 (Moore’s Law) [1] 。而英特爾雙核 Itanium

2 處理器於2006年發佈時,它的微處理器已經超過十億個電晶體,也就是超過約一百萬倍英特爾第一款的微處理器4004 [2] 。2011年,英特爾推出了革命性的、被稱為三柵極

(Tri-Gate) 的3-D電晶體設計,以提高性能和省電能力 [3];而這也是CPU又一個的里程碑。其中,CPU的性能是高度倚賴作為平衡輸入和消耗功率的電壓調節器

(VR)。為此,立錡已經提出了數種 VR 控制器,以滿足每一代CPU的規格。以下將顯示兩者之間的對應表。

1.2. 電壓調節器 (VR )

隨著微處理器變得越來越強大,功耗也顯著地增加。為了滿足微處理器的高電流和低電壓的電源需求,因此使用了多相位的電壓調節器

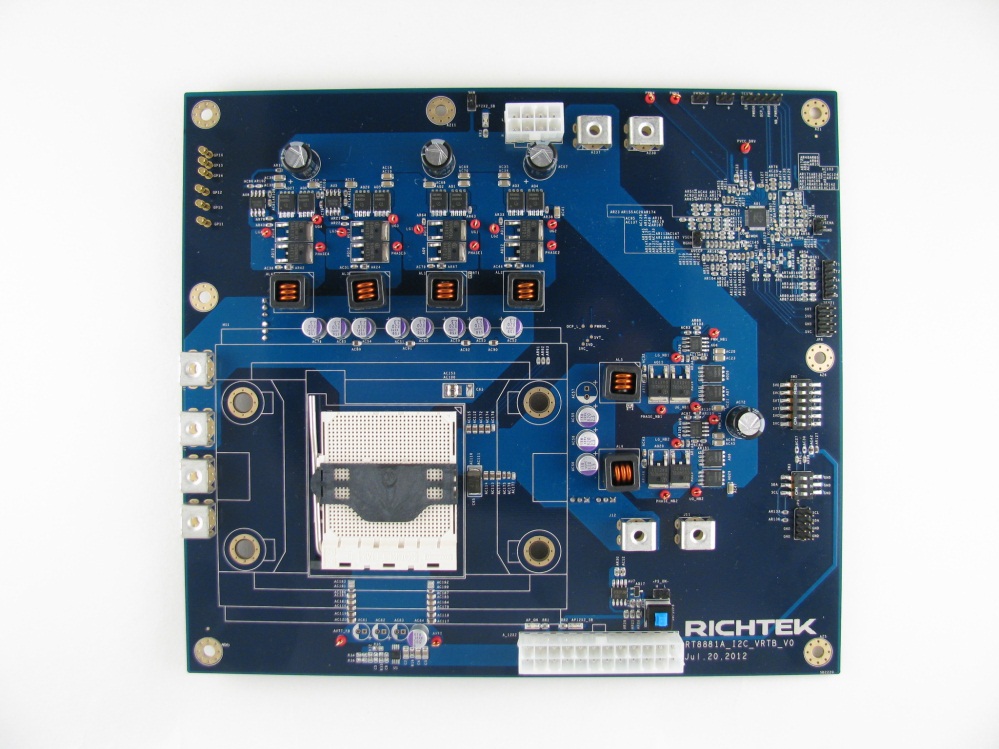

(VR)。圖一是立錡針對不同CPU的模擬板。圖一(a) 顯示 AMD SVI2 處理器的CPU電源解決方案,而圖一(b) 顯示英特爾 VR12.5處理器的CPU電源解決方案。

|

|

|

|

(a)

|

(b)

|

圖一、立錡的CPU模擬板。 (a) AMD SVI2 處理器, (b) 英特爾 VR12.5處理器。

一般來說,VR是採用電壓模式控制的交插式多相位同步降壓轉換器。不過,現今 VR面臨了更嚴苛的挑戰,不僅需要高電流,還有嚴格的瞬態響應要求。為了使系統能有更快速的響應,並且也減少尺寸和成本,立錡提出了

G-NAVP™ 架構的多相位 VR。表一至表四所示為立錡的 VR 控制器與不同 CPU功率規格之間的對應表。

表一、立錡的 VR 控制器,用於 AMD K8/K8_M2 / 英特爾 VR10.x & VR11.x

的CPU電源解決方案

|

控制器型號

|

RT8857A

|

RT8862

|

|

相位數

|

4/3/2/1 相位

|

4/3/2/1 相位

|

|

內建驅動器數量

|

2

|

2

|

|

控制架構

|

電壓模式

|

電壓模式

|

|

封裝

|

WQFN-48L 7x7

|

WQFN-48L 7x7

|

表二、立錡的 VR 控制器,用於英特爾 VR12 的CPU電源解決方案

|

控制器型號

|

RT8859A/M

|

RT8876A

|

|

相位數

|

4/3/2/1 + 1相位

|

3/2/1 + 1相位

|

|

內建驅動器數量

|

0 + 0

|

3 + 0

|

|

控制架構

|

G-NAVP™

|

G-NAVP™

|

|

封裝

|

WQFN-56L 7x7

|

WQFN-56L 7x7

|

表三、立錡的 VR 控制器用於英特爾 VR12.5 的CPU電源解決方案

|

控制器型號

|

RT8883A

|

RT8889A

|

RT8884A

|

|

相位數

|

2/1相位

|

3/2/1相位

|

4/3/2/1相位

|

|

內建驅動器數量

|

2

|

3

|

0

|

|

控制架構

|

G-NAVP™

|

G-NAVP™

|

G-NAVP™

|

|

封裝

|

WQFN-32L 4x4

|

WQFN-40L 5x5

|

WQFN-32L 4x4

|

表四、立錡的 VR 控制器用於AMD SVI2 的CPU電源解決方案

|

控制器型號

|

RT8877C/D

|

RT8878A/B

|

RT8881A

|

RT8894A

|

|

相位數

|

4/3/2/1 + 2/1/0相位

|

4/3/2/1 + 2/1/0相位

|

4/3/2/1 + 2/1/0相位

|

4/3/2/1 + 2/1/0相位

|

|

內建驅動器數量

|

0 + 0

|

2 + 0

|

2 + 0

|

3 + 0

|

|

I2C 介面

|

N/A

|

N/A

|

支援

|

支援

|

|

控制架構

|

G-NAVP™

|

G-NAVP™

|

G-NAVP™

|

G-NAVP™

|

|

封裝

|

WQFN-52L 6x6

|

WQFN-52L 6x6

|

WQFN-52L 6x6

|

WQFN-56L 7x7

|

2. G-NAVP™ 架構之簡介

G-NAVP™ 架構是一種具有電流斜坡和AVP功能的漣波型固定導通時間的控制架構。固定導通時間控制的特點是在保持重載的高效率時,也提高輕載的效率,以滿足越來越嚴格的輕載效率規格。增強的輕載效率能提高手機產品的使用時間,這對消費使用者是非常重要的特點。AVP功能則是為了節省能源和

BOM 成本,而這也是由CPU晶片製造商,如英特爾和AMD,所規定的功能。

G-NAVP™ 是「綠能原生適應性電壓定位」的縮寫。G-NAVP™架構提供了許多值得注意的特點:

- 對所有VR 之AVP的要求,很容易設定其負載線(下垂)

- 快速的瞬態響應,從而降低了輸出電容值和成本

- 輕載時的高效率

- 對所有VR 之DC的要求,都有高輸出電壓準確度

- 對所有VR 之漣波的要求,都能使用固定電流漣波

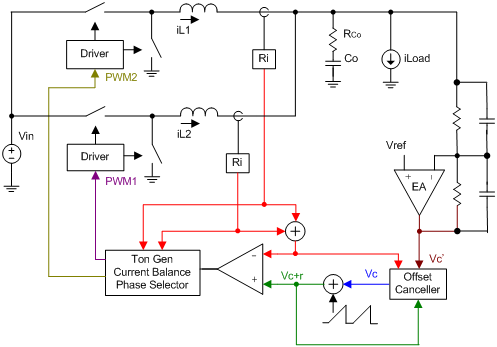

圖二為 G-NAVP™ 架構的電路示意圖。G-NAVP™ 架構是具有外部斜坡 (ramp)

和DC偏移消除的一種固定導通時間之電流模式控制。具有限DC增益的誤差放大器 (EA) 可用來調整AVP負載線,並作為極點和零點補償。電流信號是透過 DCR

電流檢測網路,並用外部斜坡 (ramp) 和 comp信號來調變;其中加上外部斜坡 (ramp) 是為了增加抗雜訊能力。導通時間產生器 (on-time

generator) 將隨輸入和輸出電壓自動改變導通時間,以使電感器電流漣波在整個輸入 / 輸出範圍都保持恆定。為能有更精確的輸出電壓,在迴路中加上DC偏移消除功能好消除漣波偏移電壓。上述提及的功能不僅增加CPU控制器的穩健性和精確度,而且能保有良好的瞬態響應性能。

圖二、G-NAVP™ 控制架構之電路圖

2.1. 固定導通時間控制的調變

由於固定導通時間控制有較快的瞬態響應,良好的輕載效率和更小的組件尺寸,使得它已被廣泛採用。對於時下的手機產品,較長的使用時間對消費使用者是很重要的特性之一。因此,固定導通時間控制所具有的良好的輕載效率,非常能滿足手機設計者的需求。

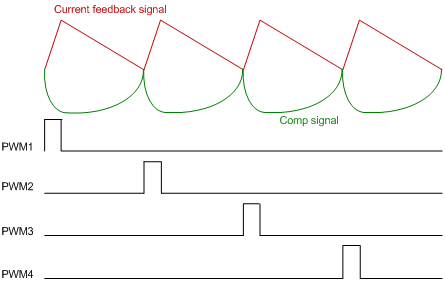

固定導通時間控制也是一種變頻控制。PWM是在連續電流模式(CCM)下,透過current feedback 信號和

comp信號來調變的,如圖三所示。當comp 信號上升碰到 current feedback信號時,控制開關打開;經過內部單次觸發定時器的時間期滿後才關閉。

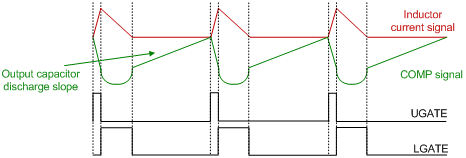

圖三、在CCM時,基本 G-NAVP™ 調變波形示意圖

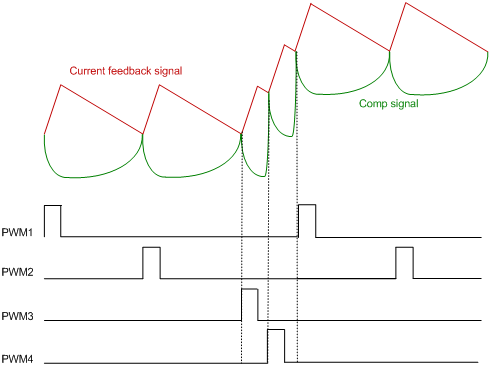

在負載的瞬態變化中,固定導通時間控制會自動改變開關頻率,以加快瞬態響應。當負載上升的瞬態變化時,關閉時間減少,相當於提高了開關頻率,所以將更多的能量傳送給輸出負載,如圖四。此外,對於負載下降的瞬態變化時,關閉時間增加,相當於降低開關頻率,也同時緩和了過衝現象。

圖四、在負載上升時,G-NAVP™ 的調變示意圖

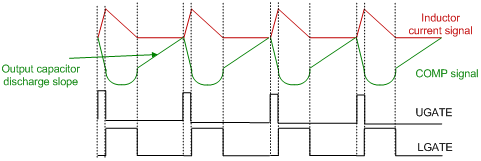

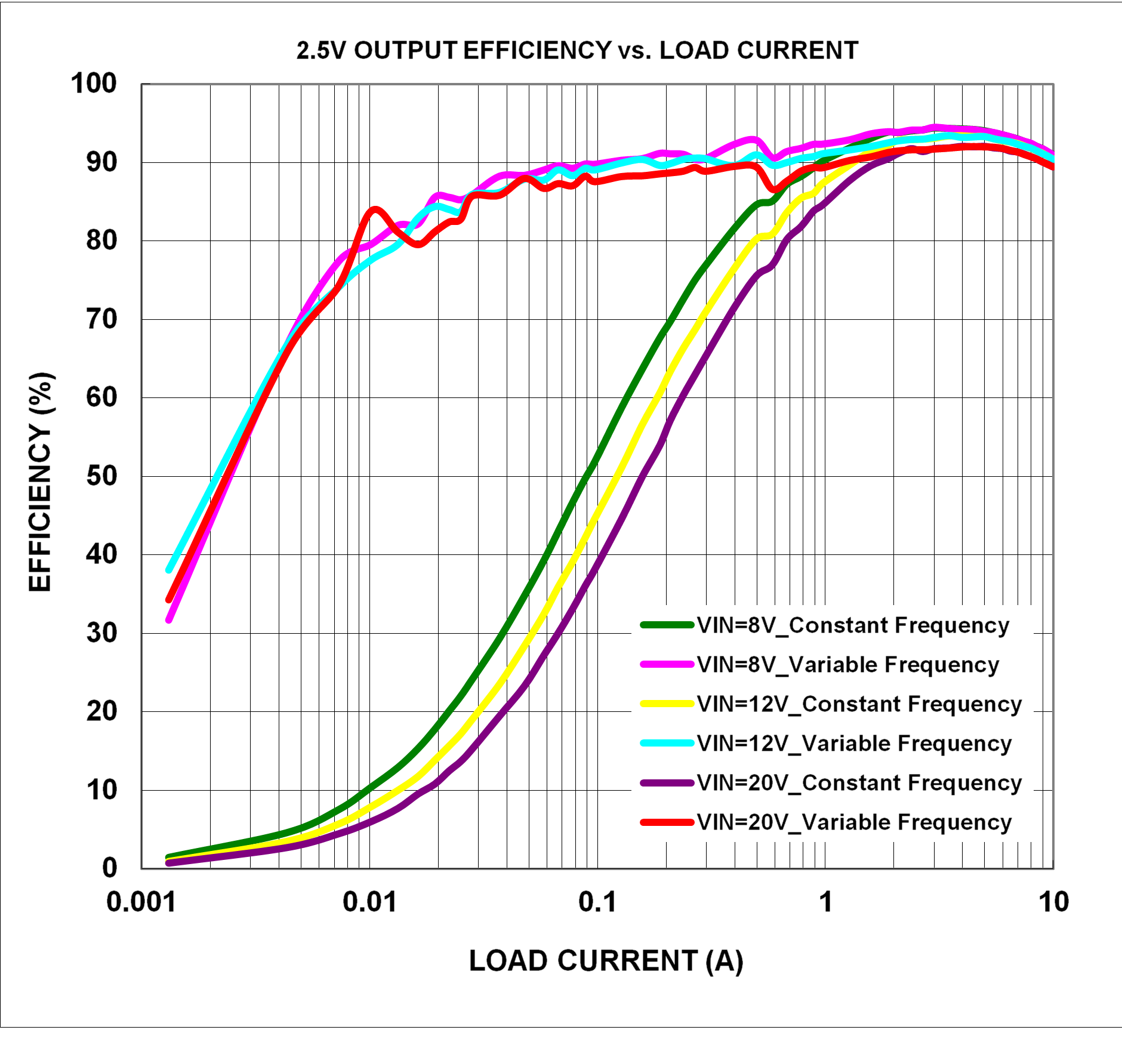

固定導通時間控制的主要優點是它的輕載效率。在非連續電流模式(DCM)下,固定導通時間控制的開關頻率是和負載電流成正比,如圖五所示。在輕載時,開關損耗即為主要的損耗,所以輕載效率可藉由降低開關頻率而得到改善。在圖六可以看到在輕載條件下,使用固定導通時間控制可比使用定頻控制達到更高的效率。

在 DCM 操作中,低側的MOSFET 如同一個二極體;在電感器電流達到零時,低側的 MOSFET 才會關閉。低側的 MOSFET 被關閉之後,輸出電容的放電時間就取決於負載電流。

(a) 較輕的負載時電容放電斜率較圖五 (b) 低。

(b) 負載增加時電容放電斜率較圖五 (a) 高。

圖五、在 DCM 下,G-NAVP™ 控制的波形示意圖;(a) 較輕的負載時,(b) 負載增加時。

圖六、定頻控制與變頻控制的效率比較圖。

2.2. 固定電流漣波

由於在導通時間內,電感電流漣波正比於輸入電壓和輸出電壓之差,電感電流漣波會隨輸入電壓和輸出電壓而變化,並進一步影響輸出電壓漣波。

(1)

(1)

固定電流漣波之固定導通時間(CCRCOT)機制會檢測輸入和輸出電壓,並自動使導通時間和輸入和輸出電壓之差成反比。以此導通時間控制法,G-NAVP™

架構可以在寬輸入 / 輸出操作範圍內提供絕佳的輸出電壓漣波,並能通過輸出漣波TOB規格,也可以進一步降低輸出電容的尺寸。

2.3. 適應性電壓定位

目前消費性電子產品的趨勢是將產品設計得越來越小;然而,電源供應器的大小通常須視功率級的元件,如電感和電容之大小而定。此外,當元件尺寸變小後,散熱問題就更為突顯。適應性電壓定位

(AVP)功能具備節省能源和 BOM 成本的特色,於是為了解決上述問題而被提出。

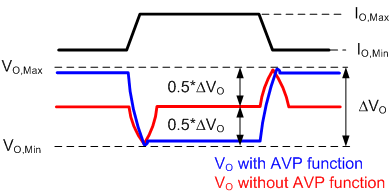

AVP 的基本原理是將輸出電壓值控制在比滿載時最小電壓值略高,而比輕負載時最大電壓值略低。因此,在瞬態變化期間,整個電壓容差範圍可作為的電壓跳升或下降的範圍。圖七顯示非

AVP 和 AVP 設計之間的瞬態變化的比較圖 [4] - [5] 。因此,AVP 的設計能夠使用較少的輸出電容,降低 VR 的成本。此外,AVP 控制也使散熱設計較為容易,因為在滿載時

VR 的輸出功率已降低了。

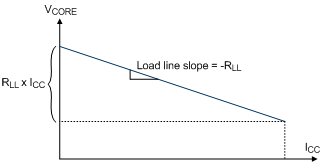

要實現 AVP 功能時,必須將 VR 輸出阻抗設計為固定的,如圖八所示。

圖七、AVP 的功能示意圖

圖八、負載電流與輸出電壓的關係

G-NAVP™ 架構不採用較複雜的類型三 (type-3) 補償器,反而採用低增益的補償器(有一個極點和一個零點);且藉著低增益補償中原生的穩態誤差,來實現

AVP 功能。也因此,此架構被稱為原生適應性電壓定位(NAVP)控制架構。

在G-NAVP™ 架構中,AVP的功能的運作則須設定經電流迴路和電壓迴路之負載線(下垂)。為使用戶能方便使用,立錡在這些

IC 的規格書中都提供了相對應的簡要負載線設定公式。

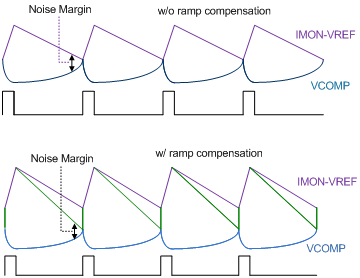

2.4. 斜坡補償

G-NAVP™ 架構因考慮到雜訊邊限和抖動,所以採用了斜坡補償,以增加在開關節點的抗雜訊能力

(noise immunity) ,並減少抖動 (jitter) 。此外,藉適當的設計,斜坡補償也可使模式的切換較為平順。圖九顯示有和無斜坡補償的雜訊邊限之比較。

圖九、有和無斜坡補償的雜訊邊限之比較。

3. 結論

隨著行動產品市場的增長,電池有限的使用時間和散熱等因素使得電源效率的問題愈來愈被重視;立錡所提供的G-NAVP™

架構則能兼顧性能和效率的要求,非常符合消費者的需要。

G-NAVP™ 架構採用的是有電流斜坡和AVP功能的漣波型固定導通時間控制法。固定導通時間控制具有快速響應和高效率的特點、AVP

能節省 BOM 的成本、偏移取消電路和斜坡補償則能提高DC的精確度和抗雜訊能力。結合上述功能,以 G-NAVP™ 為控制架構的VR控制器能提供絕佳的性能,且可滿足大多數英特爾和AMD

之 VR 電源規格。

4. 參考資料

|

[1]

|

Intel document, “Moore’s Law Timeline,” Available

at

http://download.intel.com/pressroom/kits/events/moores_law_40th/MLTimeline.pdf

|

|

[2]

|

Intel document, “Intel Processor History,” Available

at

http://download.intel.com/pressroom/kits/IntelProcessorHistory.pdf

|

|

[3]

|

Intel document, “Intel®’s 22nm Technologys

Moves Transistor Into the 3rd Dimension,” Available at

http://www.intel.com/content/dam/www/public/us/en/documents/backgrounders/standards-22-nanometers-technology-backgrounder.pdf

|

|

[4]

|

Kaiwei Yao, Yuancheng Ren, Julu Sun, Kisun Lee,

Ming Xu, Jinghai Zhou and Fred C. Lee, “Adaptive Voltage Position Design

for Voltage Regulators,” IEEE APEC’04.

|

|

[5]

|

Jian Rong Huang, Sophia Chien-Hui Wang, Chia Jung

Lee, Eddie Kuo-Lung Tseng and Dan Chen, “Native AVP Control Method for

Constant Output Impedance of DC Power Converters,” IEEE PESC’07.

|